MT9P012: 1/3.2-Inch 5Mp Digital Image Sensor Addendum Introduction

# **Electrical Characteristics Data Sheet** Addendum

### MT9P012

For more information, refer to the data sheet on Micron's Web site: www.micron.com/imaging

### Introduction

This document supplements Micron's MT9P012 CMOS digital image sensor preliminary data sheet (Revision B, 07/09/2007) with the register list and default values, and the register descriptions tables. The standard CMOS image sensor data sheet should be referenced for a complete description of this 1/3.2-inch 5Mp digital image sensor.

#### Table 1: **Key Performance Parameters**

| Parameter          |                                  | Value                                                            |  |  |

|--------------------|----------------------------------|------------------------------------------------------------------|--|--|

| Optical format     |                                  | 1/3.2-inch (4:3)                                                 |  |  |

| Active imager size |                                  | 4.54mm(H) x 3.40mm(V)                                            |  |  |

|                    |                                  | 5.67mm diagonal                                                  |  |  |

| Active pixels      |                                  | 2592H x 1944V                                                    |  |  |

| Pixel size         |                                  | 1.75 x 1.75μm                                                    |  |  |

| Chief ray angle    |                                  | 6°, 15.3°, 22.7°, 25.0°                                          |  |  |

| Color filter array |                                  | RGB Bayer pattern                                                |  |  |

| Shutter type       |                                  | Electronic rolling shutter (ERS) with global reset release (GRR) |  |  |

| Input clock freque | ency                             | 2–64 MHz                                                         |  |  |

|                    | Parallel                         | 96 Mp/s at 96 MHz PIXCLK                                         |  |  |

| Maximum data       | CCP2                             | 650 Mb/s                                                         |  |  |

| rate               | MIPI                             | 768 Mb/s per lane                                                |  |  |

| Frame rate         | Full resolution<br>(2592 x 1944) | 15 fps                                                           |  |  |

|                    | VGA (640 x 480)                  | 640H x 480V with 2X skip and 2X bin: 70 fps                      |  |  |

| ADC resolution     |                                  | 12-bit, on-die                                                   |  |  |

| Responsivity       |                                  | 0.39 V/lux-sec (550nm)                                           |  |  |

| Dynamic range      |                                  | 62.8dB                                                           |  |  |

| SNR <sub>MAX</sub> |                                  | 40.4dB                                                           |  |  |

|                    | I/O digital                      | 1.7–1.9V (1.8V nominal), or 2.4–3.1V (2.8V nominal)              |  |  |

| Supply voltage     | Digital                          | 1.7–1.9V (1.8V nominal)                                          |  |  |

|                    | Analog                           | 2.4–3.1V (2.8V nominal)                                          |  |  |

| Power              | Full resolution                  | 534mW at 55°C                                                    |  |  |

| consumption        | Standby                          | 228µW at 55°C (TYP, EXTCLK disabled)                             |  |  |

| Package            |                                  | Bare die                                                         |  |  |

| Operating temper   | ature                            | –30°C to +70°C (at junction)                                     |  |  |

PDF: 09005aef82e3c29b/Source: 09005aef82e3c263 MT9P012\_ADD\_B .fm - Rev. B 12/07 EN

Micron Technology, Inc., reserves the right to change products or specifications without notice. ©2007 Micron Technology, Inc. All rights reserved.

1 ‡Products and specifications discussed herein are for evaluation and reference purposes only and are subject to change by Micron without notice. Products are only warranted by Micron to meet Micron's production data sheet specifications.

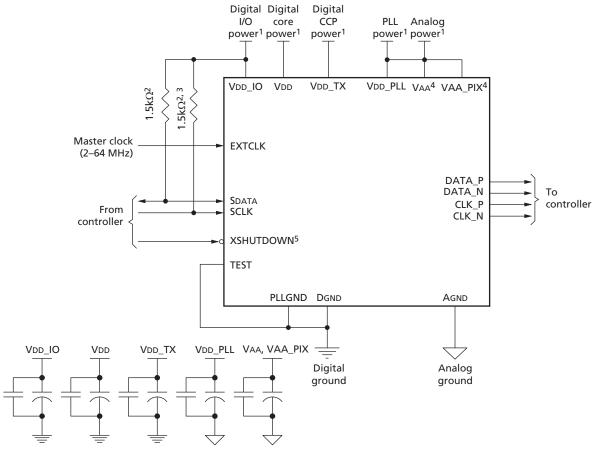

## Typical Connections (CCP)

Figure 3 below and Figure 4 on page 3 show typical connection schematics for the MT9P012 die.

#### Figure 3: Typical Connection: Serial CCP2 Pixel Data Interface

Notes: 1. All power supplies should be adequately decoupled.

- 2. Micron recommends a resistor value of  $1.5k\Omega$ , but a greater value may be used for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 4. VAA and VAA\_PIX must be tied together.

- 5. Also referred to as RESET\_BAR.

- 6. VPP, which can be used during the module manufacturing process, is not shown in Figure 3. This pad is left unconnected during normal operation.

- 7. The parallel interface output pads can be left unconnected if the serial output interface is used.

- Micron recommends that 0.1µF and 1µF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations.

- 9. TEST must be tied to DGND.

- 10. Micron recommends that PLLGND be tied to DGND.

- 11. VDD\_TX must be tied to VDD.

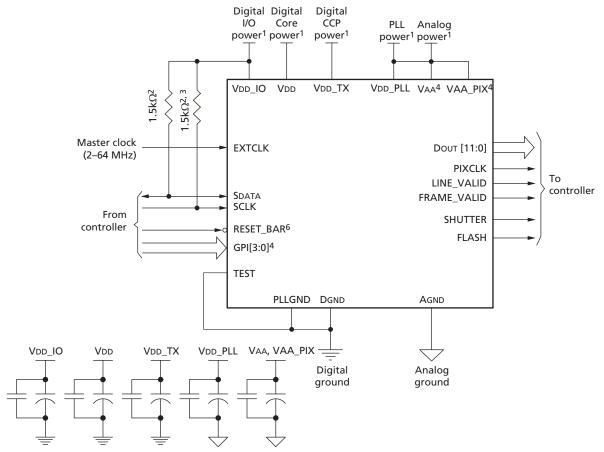

#### MT9P012: 1/3.2-Inch 5Mp Digital Image Sensor Addendum Typical Connections (CCP)

#### Figure 4: Typical Connection: Parallel Pixel Data Interface (CCP2)

- Notes: 1. All power supplies should be adequately decoupled.

- 2. Micron recommends a resistor value of  $1.5k\Omega$ , but a greater value may be used for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- The GPI pins can be either statically pulled HIGH/LOW to be used as module IDs, or they can be programmed to perform special functions (TRIGGER, OE\_N, SADDR, STANDBY) to be dynamically controlled.

- 5. VAA and VAA\_PIX must be tied together.

- 6. Also referred to as XSHUTDOWN.

- 7. VPP, which can be used during the module manufacturing process, is not shown in Figure 4. This pad is left unconnected during normal operation.

- 8. The serial interface output pads can be left unconnected if the parallel output interface is used.

- Micron recommends that 0.1µF and 1µF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations.

- 10. TEST must be tied to DGND.

- 11. Micron recommends that PLLGND be tied to DGND.

- 12. VDD\_TX must be tied to VDD.

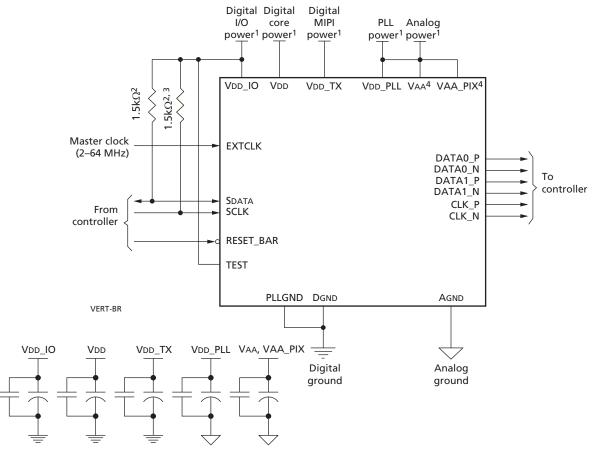

## **Typical Connections (MIPI)**

Figure 5 and Figure 6 on page 5 show typical connection schematics for the MT9P012 die.

#### Figure 5: Typical Connection: Serial MIPI Pixel Data Interface

Notes: 1. All power supplies should be adequately decoupled.

- 2. Micron recommends a resistor value of  $1.5k\Omega$ , but a greater value may be used for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 4. VAA and VAA\_PIX must be tied together.

- 5. VPP, which can be used during the module manufacturing process, is not shown in Figure 5. This pad is left unconnected during normal operation.

- 6. The parallel interface output pads can be left unconnected if the serial output interface is used.

- Micron recommends that 0.1µF and 1µF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations.

- 8. TEST must be tied to VDD\_IO.

- 9. Micron recommends that PLLGND be tied to DGND.

- 10. VDD\_TX must be tied to VDD.

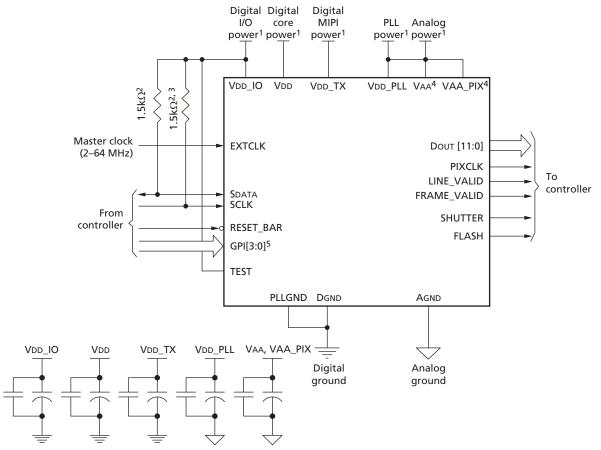

#### MT9P012: 1/3.2-Inch 5Mp Digital Image Sensor Addendum Typical Connections (MIPI)

#### Figure 6: Typical Connection: Parallel Pixel Data Interface (MIPI)

Notes: 1. All power supplies should be adequately decoupled.

- 2. Micron recommends a resistor value of  $1.5k\Omega$ , but a great value may be used for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 4. VAA and VAA\_PIX must be tied together.

- 5. The GPI pins can be either statically pulled HIGH/LOW to be used as module IDs, or they can be programmed to perform special functions (TRIGGER, OE\_N, SADDR, STANDBY) to be dynamically controlled.

- 6. VPP, which can be used during the module manufacturing process, is not shown in Figure 6. This pad is left unconnected during normal operation.

- 7. The serial interface output pads can be left unconnected if the parallel output interface is used.

- Micron recommends that 0.1µF and 1µF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations.

- 9. TEST must be tied to VDD\_IO.

- 10. Micron recommends that PLLGND be tied to DGND.

- 11. VDD\_TX must be tied to VDD.

### **Electrical Characteristics**

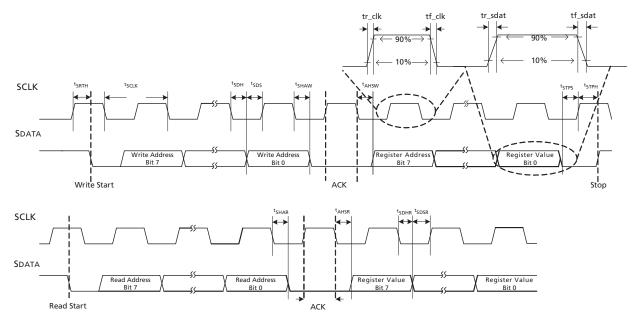

#### **Two-Wire Serial Register Interface**

The electrical characteristics of the two-wire serial register interface (SCLK, SDATA) are shown in Figure 58 and Table 33. The SCLK and SDATA signals feature fail-safe input protection, Schmitt trigger input, and suppression of input pulses of less than 50ns.

Figure 58: Two-Wire Serial Bus Timing Parameters

Note: Read sequence: For an 8-bit READ, read waveforms start after WRITE command and register address are issued.

#### Table 33: Two-Wire Serial Register Interface Electrical Characteristics

| Definition            | Condition                                    | Symbol | Min  | Тур   | Мах          | Unit |

|-----------------------|----------------------------------------------|--------|------|-------|--------------|------|

| Input LOW voltage     |                                              | VIL    | 0.73 |       | 0.3 x VDD_IO | V    |

| Input leakage current | No pull up resistor;<br>VIN = VDD_IO or DGND | lin    | -2   |       | 2            | μA   |

| Output LOW voltage    | At specified 3mA                             | Vol    | 0.11 | 0.147 | 0.275        | V    |

| Output LOW current    | At specified VoL 0.1V                        | IOL    |      |       | 3            | mA   |

| Input pad capacitance |                                              | CIN    |      |       | 6            | pF   |

| Load capacitance      |                                              | CLOAD  |      |       |              | pF   |

#### Table 34: Two-Wire Serial Register Interface Timing Specification

<sup>f</sup>EXTCLK = 24 MHz; VDD = 1.8V; VDD\_IO = 1.8V; VAA = 2.8V; VAA\_PIX = 2.8V; VDD\_PLL = 2.8V; Output load = 68.5pF; TJ = 55°C

| Symbol            | Definition                    | Condition              | Min  | Тур | Мах  | Unit |

|-------------------|-------------------------------|------------------------|------|-----|------|------|

| <sup>f</sup> SCLK | Serial interface input clock  | -                      | 100  |     | 400  | kHz  |

| <sup>t</sup> SCLK | Serial interface input period | VCMF                   | 2.5  |     | 10   | µsec |

|                   | SCLK duty cycle               | Vod                    | 45   | 50  | 60   | %    |

| <sup>t</sup> R    | SCLK/SDATA rise time          |                        |      |     | 300  | µsec |

| <sup>t</sup> SRTS | Start setup time              | Master WRITE to slave  | 0.6  |     |      | µsec |

| <sup>t</sup> SRTH | Start hold time               | Master WRITE to slave  | 0.3  |     |      | µsec |

| <sup>t</sup> SDH  | Sdata hold                    | Master WRITE to slave  | 0.3  |     | 0.65 | µsec |

| <sup>t</sup> SDS  | SDATA setup                   | Master WRITE to slave  | 0.3  |     |      | µsec |

| <sup>t</sup> SHAW | SDATA hold to ACK             | Master READ to slave   | 0.15 |     | 0.65 | µsec |

| <sup>t</sup> AHSW | ACK hold to SDATA             | Master WRITE to slave  | 0.15 |     | 0.65 | µsec |

| <sup>t</sup> STPS | Stop setup time               | Master WRITE to slave  | 0.3  |     |      | µsec |

| <sup>t</sup> STPH | Stop hold time                | Master WRITE to slave  | 0.6  |     |      | µsec |

| <sup>t</sup> SHAR | SDATA hold to ACK             | Master WRITE to slave  | 0.3  |     | 0.65 | µsec |

| <sup>t</sup> AHSR | ACK hold to SDATA             | Master WRITE to slave  | 0.3  |     | 0.65 | µsec |

| <sup>t</sup> SDHR | Sdata hold                    | Master READ from slave | 0.3  |     | 0.65 | µsec |

| <sup>t</sup> SDSR | SDATA setup                   | Master READ from slave | 0.3  |     |      | µsec |

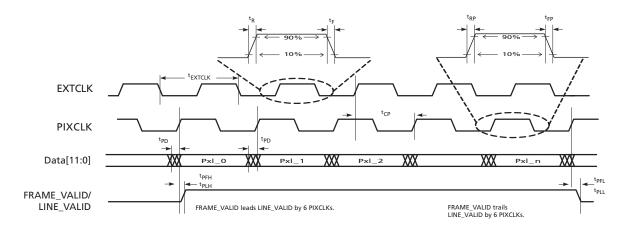

#### Figure 59: Parallel Data Output Timing Diagram

Notes: 1. PLL disabled for <sup>t</sup>CP.

#### EXTCLK

The electrical characteristics of the EXTCLK input are shown in Table 35. The EXTCLK input supports an AC-coupled sine-wave input clock or a DC-coupled square-wave input clock.

If EXTCLK is AC-coupled to the MT9P012 and the clock is stopped, the EXTCLK input to the MT9P012 must be driven to ground or to VDD\_IO. Failure to do this will result in excessive current consumption within the EXTCLK input receiver.

#### Table 35: Electrical Characteristics (EXTCLK)

| Definition                                           | Condition             | Symbol                  | Min          | Тур  | Max          | Unit    |

|------------------------------------------------------|-----------------------|-------------------------|--------------|------|--------------|---------|

| Input clock frequency                                | PLL enabled           | <sup>f</sup> EXTCLK1    | 6            |      | 48           | MHz     |

| Input clock period                                   | PLL enabled           | <sup>t</sup> EXTCLK1    | 21           |      | 167          | ns      |

| Input clock rise slew rate                           |                       | <sup>t</sup> R          | 1            |      |              | V/ns    |

| Input clock fall slew rate                           |                       | <sup>t</sup> F          | 1            |      |              | V/ns    |

| Input clock minimum voltage swing<br>(AC coupled)    |                       | VIN_AC                  | 0.5          |      |              | V (p-p) |

| Input clock maximum voltage swing<br>(DC coupled)    |                       | Vin_dc                  |              |      | VDD_IO + 0.5 | V       |

| Input clock signalling frequency<br>(low amplitude)  | VIN =<br>VIN_AC (MIN) | <sup>†</sup> CLKMAX(AC) |              |      | 27           | MHz     |

| Input clock signalling frequency<br>(full amplitude) | VIN = VDD_IO          | <sup>†</sup> CLKMAX(DC) |              |      | 48           | MHz     |

| Clock duty cycle                                     |                       |                         | 45           | 50   | 55           | %       |

| Input clock jitter                                   | cycle-to-cycle        | <sup>t</sup> JITTER     | 15.8         | 20.5 | 27.4         | ps      |

| PLL VCO lock time                                    |                       | <sup>t</sup> LOCK       |              |      |              | ms      |

| Input pad capacitance                                |                       | CIN                     |              |      |              | рF      |

| Input HIGH leakage current                           |                       | Іін                     | -10          |      | 10           | μA      |

| Input HIGH voltage                                   |                       | Vih                     | VDD_IO x 0.7 |      | VDD_IO + 0.5 | V       |

| Input LOW voltage                                    |                       | VIL                     | -0.5         |      | 0.3 x VDD_IO | V       |

#### **Parallel Pixel Data Interface**

The electrical characteristics of the parallel pixel data interface (FV, LV, DOUT[11:0], PIXCLK, SHUTTER, and FLASH outputs) are shown in Table 36.

#### Table 36: Electrical Characteristics (Parallel Pixel Data Interface)

| Definition                       | Condition                                                           | Symbol              | Min  | Тур  | Мах  | Unit |

|----------------------------------|---------------------------------------------------------------------|---------------------|------|------|------|------|

| Output HIGH voltage              | At specified IOH 8mA                                                | Voн                 | 1.4  | 1.61 | 1.63 | V    |

| Output LOW voltage               | At specified IOL 8mA                                                | Vol                 | 0.06 | 0.07 | 0.1  | V    |

| Output HIGH current              | At specified Voн, VDD_IO = 1.8V                                     | Іон                 | -14  |      | -12  | mA   |

| Output LOW current               | At specified VoL = 0.3V                                             | IOL                 | 6    |      | 10   | mA   |

| Output LOW current               | At specified VoL = 0.4V                                             | IOL                 | 8    |      | 13   | mA   |

| Tri-state output leakage current |                                                                     | loz                 | 0.1  |      | 0.2  | μA   |

| Output pin slew (rising)         | Default slew rate register settings,<br>CLOAD = 35pF, 64 MHz PIXCLK |                     |      | 0.29 |      | V/ns |

| Output pin slew (falling)        | Default slew rate register settings,<br>CLOAD = 35pF, 64 MHz PIXCLK |                     |      | 0.4  |      | V/ns |

| PIXCLK to data valid             | 60 MHz PIXCLK                                                       | <sup>t</sup> PD     |      | 4    | 16   | ns   |

| PIXCLK frequency                 | Default                                                             | <sup>f</sup> PIXCLK |      | 60   | 96   | MHz  |

| PIXCLK to FV HIGH                | 60 MHz PIXCLK                                                       | <sup>t</sup> PFH    |      | 4    | 6    | ns   |

| PIXCLK to LV HIGH                | 60 MHz PIXCLK                                                       | <sup>t</sup> PLH    |      | 3    | 5    | ns   |

| PIXCLK to FV LOW                 | 60 MHz PIXCLK                                                       | <sup>t</sup> PFL    |      | 4    | 6    | ns   |

| PIXCLK to LV LOW                 | 60 MHz PIXCLK                                                       | <sup>t</sup> PLL    |      | 4    | 6    | ns   |

#### **Serial Pixel Data Interface**

The electrical characteristics of the serial pixel data interface (CLK\_P, CLK\_N, DATA0\_P, DATA1\_P, DATA0\_N, and DATA1\_N) are shown in Table 37 and Table 38.

To operate the serial pixel data interface within the electrical limits of the CSI-2 and CCP2 specifications, VDD\_IO (I/O digital voltage) is restricted to operate in the range 1.7–1.9V.

#### Table 37: Electrical Characteristics (Serial CCP2 Pixel Data Interface)

| Definition                                               | Condition | Symbol         | Min | Тур   | Мах        | Unit |

|----------------------------------------------------------|-----------|----------------|-----|-------|------------|------|

| Operating frequency                                      |           |                |     |       | 650        | MHz  |

| Fixed common mode voltage                                |           | VCMF           |     | 0.85  |            | V    |

| Differential voltage swing                               |           | Vod            |     | 142.7 |            | mV   |

| Differential current swing                               |           |                |     |       |            | mA   |

| Drive current range                                      |           |                |     |       |            | mA   |

| Drive current variation                                  |           |                |     |       |            | %    |

| Output impedance                                         |           |                |     | 66.3  |            | Ω    |

| Output impedance mismatch                                |           |                |     | 2.5   |            | %    |

| Clock Duty cycle at 416 MHz                              |           |                |     | 51    |            | %    |

| Rise time (20–80%)                                       |           | <sup>t</sup> R |     | 198.2 |            | ps   |

| Fall time (20–80%)                                       |           | fR             |     | 201.3 |            | ps   |

| Differential skew                                        |           |                |     | 26.2  |            | ps   |

| Channel to channel skew                                  |           |                |     |       | 100        | ps   |

| Maximum data rate<br>Data/strobe mode<br>Data/clock mode |           |                |     |       | 650<br>208 | Mb/s |

| Power supply rejection ratio (0–100 MHz)                 |           |                |     |       |            |      |

#### Table 38: Electrical Characteristics (Serial MIPI Pixel Data Interface)

| Definition                                                   | Symbol              | Min | Тур | Мах   | Unit  |

|--------------------------------------------------------------|---------------------|-----|-----|-------|-------|

| High speed transmit differential voltage                     | Vod                 |     |     | 152   | mV    |

| High speed transmit static common-mode voltage               | VCMTX               |     |     | 213.7 | mV    |

| Vod mismatch when output is Differential-1 or Differential-0 | ΔVod                |     |     | 0.63  | mV    |

| High speed output HIGH voltage                               | ΔVCMTX              |     |     | 0.44  | mV    |

| Single ended output impedance                                | Zos                 |     |     | 185.4 | Ω     |

| Single ended output impedance mismatch                       | ∆Zos                |     |     | 54.26 | Ω     |

| Common-level variation between 50–450 MHz                    | $\Delta VCMTX(L,F)$ |     |     | 4.24  | %     |

| Rise time (20–80%)                                           | <sup>t</sup> R      |     |     | 363.7 | ps    |

| Fall time (20–80%)                                           | <sup>t</sup> F      |     |     | 346.5 | ps    |

| Output LOW level                                             | Vol                 |     |     | 22.4  | mV    |

| Output HIGH level                                            | Vон                 |     |     | 1.2   | V     |

| Output impedance of low power parameter                      | ZOLP                |     |     | 104.7 | Ω     |

| 15–85% rise time                                             | Trlp                |     |     | 3.8   | ns    |

| 15–85% fall time                                             | TFLP                |     |     | 6.3   | ns    |

| Slew rate (CLOAD = 5–20pF)                                   | ∆v/∆dtsr            |     |     | 293.5 | mV/ns |

| Slew rate (CLOAD = 20–70pF)                                  | ∆v/∆dtsr            |     |     | 148.1 | mV/ns |

#### **Control Interface**

The electrical characteristics of the control interface (RESET\_BAR, TEST, GPI0, GPI1, GPI2, and GPI3) are shown in Table 39.

#### Table 39: DC Electrical Characteristics (Control Interface)

| Definition            | Condition                                    | Symbol | Min          | Тур   | Мах          | Unit |

|-----------------------|----------------------------------------------|--------|--------------|-------|--------------|------|

| Input HIGH voltage    |                                              | Vih    | 0.7 x Vdd_IO |       | VDD_IO + 0.5 | V    |

| Input LOW voltage     |                                              | VIL    | -0.5         |       | 0.3 x Vdd_IO | V    |

| Input leakage current | No pull-up resistor;<br>VIN = VDD_IO or DGND | lin    | -10          | 0.147 | 10           | μA   |

| Input pad capacitance |                                              | Cin    |              |       |              | pF   |

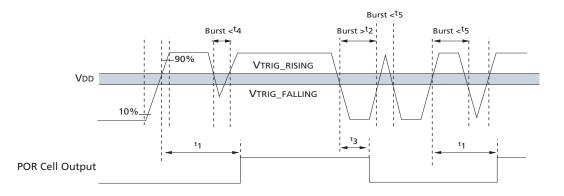

#### **Power-On Reset**

#### Table 40: Power-On Reset Characteristics

| Definition                                                                                                        | Condition                                                                                                          | Symbol         | Min | Тур | Мах | Unit |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------|-----|-----|-----|------|

| VDD rising, crossing VTRIG_RISING;<br>Internal reset being released                                               |                                                                                                                    | <sup>t</sup> 1 |     |     |     | μs   |

| VDD falling, crossing VTRIG_FALLING;<br>Internal reset active                                                     |                                                                                                                    | <sup>t</sup> 2 |     |     |     | μs   |

| Minimum VDD spike width below<br>VTRIG_FALLING; considered to be a<br>reset when POR cell output is HIGH          |                                                                                                                    | t3             |     |     |     | μs   |

| Minimum VDD spike width below<br>VTRIG_FALLING; considered to be a<br>reset when POR cell output is LOW           |                                                                                                                    | <sup>t</sup> 4 |     |     |     | μs   |

| Minimum VDD spike width above<br>VTRIG_RISING; considered to be a<br>stable supply when POR cell output<br>is LOW | While the POR cell output is LOW,<br>all VDD spikes above VTRIG_RISING<br>less than <sup>t</sup> 5 must be ignored | <sup>t</sup> 5 |     |     |     | ns   |

| VDD rising trigger voltage                                                                                        |                                                                                                                    | VTRIG_RISING   |     |     |     | V    |

| VDD falling trigger voltage                                                                                       |                                                                                                                    | VTRIG_FALLING  |     |     |     | V    |

#### Figure 60: Internal Power-On Reset

### **Operating Voltages**

VAA and VAA\_PIX must be at the same potential for correct operation of the MT9P012.

#### Table 41: DC Electrical Definitions and Characteristics

| Definition                    | Condition                     | Symbol  | Min         | Тур         | Max         | Unit |

|-------------------------------|-------------------------------|---------|-------------|-------------|-------------|------|

| Core digital voltage          |                               | Vdd     | 1.7         | 1.8         | 1.9         | V    |

| I/O digital voltage           | Parallel pixel data interface | Vdd_IO  | 1.7/2.4     | 1.8/2.8     | 1.9/3.1     | V    |

| Analog voltage                |                               | VAA     | 2.4         | 2.8         | 3.1         | V    |

| Pixel supply voltage          |                               | VAA_PIX | 2.4         | 2.8         | 3.1         | V    |

| PLL supply voltage            |                               | Vdd_PLL | 2.4         | 2.8         | 3.1         | V    |

| Digital operating current     | Streaming, full resolution    |         | 55.98       | 59.58       | 59.92       | mA   |

| I/O digital operating current | Streaming, full resolution    |         | 10.23/24.21 | 11.65/25.69 | 12.66/26.69 | mA   |

| Analog operating current      | Streaming, full resolution    |         | 121.06      | 124.98      | 127.24      | mA   |

| Pixel supply current          | Streaming, full resolution    |         | 1.57        | 1.60        | 1.62        | mA   |

| PLL supply current            | Streaming, full resolution    |         | 14.60       | 18.50       | 20.50       | mA   |

| Hard standby (clock on)       | Analog                        |         |             | 42          |             | μA   |

|                               | Digital                       |         |             | 1240/1380   |             | μA   |

| Hard standby (clock off)      | Analog                        |         |             | 12          |             | μA   |

|                               | Digital                       |         |             | 73/81       |             | μA   |

| Soft standby (clock on)       | Analog                        |         |             | 52          |             | μA   |

|                               | Digital                       |         |             | 2140/2280   |             | μA   |

| Soft standby (clock off)      | Analog                        |         |             | 12          |             | μA   |

|                               | Digital                       |         |             | 108/116     |             | μA   |

#### **Absolute Maximum Ratings**

**Caution** Stresses greater than those listed in Table 42 may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### Table 42: Absolute Maximum Values

| Definition                    | Condition           | Symbol     | Min | Тур | Max | Unit |

|-------------------------------|---------------------|------------|-----|-----|-----|------|

| Core digital voltage          |                     | Vdd_max    |     |     | 2.4 | V    |

| I/O digital voltage           |                     | VDD_IO_MAX |     |     | 2.4 | V    |

| Analog voltage                |                     | VAA        |     |     | 4   | V    |

| Pixel supply voltage          |                     | VAA_PIX    |     |     | 4   | V    |

| PLL supply voltage            |                     | Vdd_PLL    |     |     | 4   | V    |

| Digital operating current     | Worst case current  | ldd        |     |     | 90  | mA   |

| I/O digital operating current | Worst case current  | Idd_IO     |     |     | 18  | mA   |

| Analog operating current      | Worst case current  | IAA        |     |     | 145 | mA   |

| Pixel supply current          | Worst case current  | IAA_PIX    |     |     | 2   | mA   |

| PLL supply current            | Worst case current  | IDD_PLL    |     |     | 35  | mA   |

| Operating temperature         | Measure at junction | Тор        | -30 |     | 70  | °C   |

| Storage temperature           |                     | Tstg       | -40 |     | 85  | °C   |

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900 prodmktg@micron.com www.micron.com Customer Comment Line: 800-932-4992 Micron, the M logo, the Micron logo, and DigitalClarity are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

Preliminary: This data sheet contains initial characterization limits that are subject to change upon full characterization of production devices.

# **Revision History**

| Rev. B |                                                                                             |

|--------|---------------------------------------------------------------------------------------------|

| •      | Update Table 1, "Key Performance Parameters," on page 1 (input clock frequency)             |

| •      | Add Figure 3: "Typical Connection: Serial CCP2 Pixel Data Interface," on page 2             |

| •      | Add Figure 4: "Typical Connection: Parallel Pixel Data Interface (CCP2)," on page 3         |

| •      | Add Figure 5: "Typical Connection: Serial MIPI Pixel Data Interface," on page 4             |

| •      | Add Figure 6: "Typical Connection: Parallel Pixel Data Interface (MIPI)," on page 5         |

| •      | Update Table 41, "DC Electrical Definitions and Characteristics," on page 14 (Standby data) |

| •      | Update Figure 60: "Internal Power-On Reset," on page 13                                     |

| Rev. A |                                                                                             |

| •      | Initial release                                                                             |