### TN-09-92: Skipping and Binning Modes for the MT9T013 Introduction

### **Technical Note**

#### MT9T013

#### **Skipping and Binning Modes for the MT9T013**

#### **Introduction**

This technical note explains the skipping and binning modes of the Micron MT9T013 CMOS digital image sensor.

#### Skipping

The MT9T013 supports skipping, which reduces the amount of data processed by the analog signal chain in the MT9T013, allowing the frame rate to be increased. Skipping is enabled by setting x\_odd\_inc and/or y\_odd\_inc. Values of 1, 3, and 7 can be supported. Setting both of these variables to 3 reduces the amount of row and column data processed and is equivalent to the 2x2 skipping readout mode provided by the MT9T013.

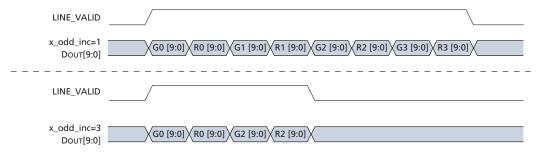

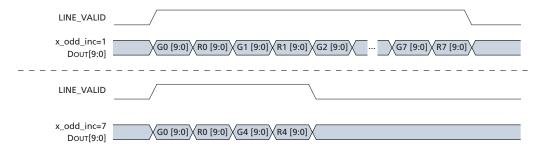

Figure 1 shows a sequence of 8 columns being read out with  $x_odd_inc = 3$  and  $y_odd_inc = 1$ .

Figure 1: Effect of x\_odd\_inc = 3 on Readout Sequence

A 1/16 reduction in resolution is achieved by setting both x\_odd\_inc and y\_odd\_inc to 7. This is equivalent to 4x4 skipping readout mode provided by the MT9T013.

# TN-09-92: Skipping and Binning Modes for the MT9T013 Skipping

Figure 2 shows a sequence of 16 columns being read out with  $x_odd_inc = 7$  and  $y_odd_inc = 1$ .

Figure 2: Effect of x\_odd\_inc = 7 on Readout Sequence

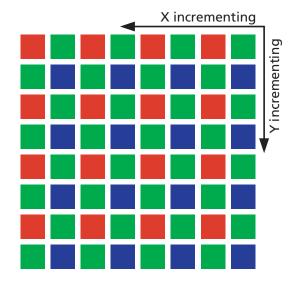

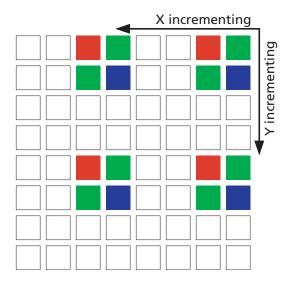

The effect of the different skipping settings on the pixel array readout is shown in Figure 3 through Figure 5 on page 3.

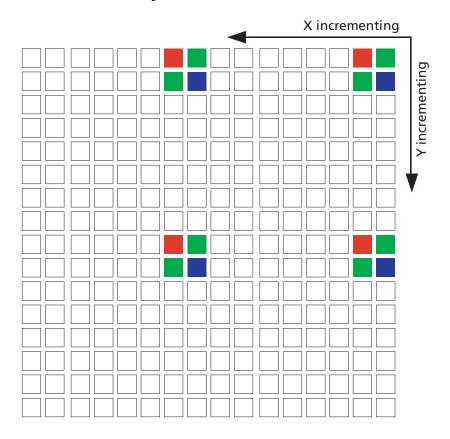

Figure 3: Pixel Readout (no subsampling)

# TN-09-92: Skipping and Binning Modes for the MT9T013 Skipping

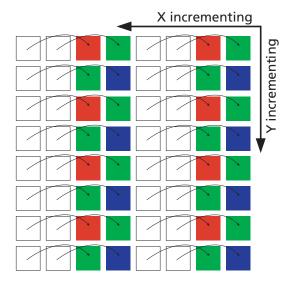

Figure 4: Pixel Readout (x\_odd\_inc = 3, y\_odd\_inc = 3)

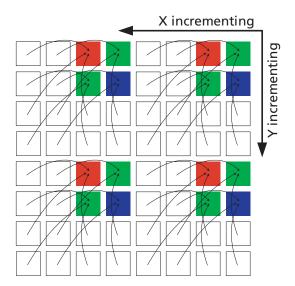

Figure 5: Pixel Readout (x\_odd\_inc = 7, y\_odd\_inc = 7)

# TN-09-92: Skipping and Binning Modes for the MT9T013 Programming Restrictions when Skipping

### **Programming Restrictions when Skipping**

When skipping is enabled in viewfinder mode and the sensor is switched back and forth between full resolution and skipping, we recommend keeping line\_length\_pck constant between the two modes. This allows the same integration times to be used in each mode.

When skipping is enabled it may be necessary to adjust the x\_addr\_end, x\_addr\_start, and y\_addr\_end, y\_addr\_start settings (the values for these registers are required to correspond with rows/columns that form part of the skipping sequence).

The adjustment should be made in accordance with the following rules:

- x\_addr\_start must be a multiple of 2

- for example, 0, 4, 6, 8, and x\_addr\_start=2 is not supported

When 2x2 skipping mode is enabled

- (x\_addr\_end x\_addr\_start + x\_odd\_inc) should be a multiple of 4

- (y\_addr\_end y\_addr\_start + y\_odd\_inc) should be a multiple of 4

When 4x4 skipping mode is enabled

- (x\_addr\_end x\_addr\_start + x\_odd\_inc) should be a multiple of 8

- (y\_addr\_end y\_addr\_start + y\_odd\_inc) should be a multiple of 8

The number of columns/rows read out with skipping can be found from the equation below:

When 2x2 skipping mode is enabled

• columns/rows = (addr\_end - addr\_start + odd\_inc) / 2

When 4x4 skipping mode is enabled

• columns/rows = (addr\_end - addr\_start + odd\_inc) / 4

#### TN-09-92: Skipping and Binning Modes for the MT9T013 Sample Register Settings for Skipping

### **Sample Register Settings for Skipping**

To get a 2048 x 1536 full resolution without skipping, the recommended register settings can be:

[full resolution starting address with (8,8)] REG=0x0104, 1 // GROUPED PARAMETER HOLD REG=0x0382, 1 // X\_ODD\_INC REG=0x0386, 1 // Y ODD INC REG=0x0344, 8 // X\_ADDR\_START REG=0x0346, 8 // Y\_ADDR\_START REG=0x0348, 2055 // X\_ADDR\_END REG=0x034A, 1543 // Y ADDR END REG=0x034C, 2048 // X\_OUTPUT\_SIZE // Y\_OUTPUT\_SIZE REG=0x034E, 1536 REG=0x0104, 0 // GROUPED\_PARAMETER\_HOLD

To achieve a 1024 x 786 resolution without 2x2 skipping, the recommended register settings can be:

```

[2x2 skipping starting address with (8,8)]

REG=0x0104, 1

// GROUPED_PARAMETER_HOLD

REG=0x0382, 3

// X_ODD_INC

REG=0x0386, 3

// Y_ODD_INC

// X ADDR START

REG=0x0344, 8

REG=0x0346, 8

// Y_ADDR_START

REG=0x0348, 2053

// X ADDR END

REG=0x034A, 1541

// Y_ADDR_END

REG=0x034C, 1024

// X_OUTPUT_SIZE

REG=0x034E, 768

// Y_OUTPUT_SIZE

REG=0x0104, 0

// GROUPED PARAMETER HOLD

```

To achieve a 512 x 384 resolution without 4x4 skipping, the recommended register settings can be:

```

[4x4 skipping starting address with (8,8)]

REG=0x0104, 1 // GROUPED_PARAMETER_HOLD

```

REG=0x0382, 7 // X ODD INC // Y\_ODD\_INC REG=0x0386, 7 REG=0x0344, 8 // X\_ADDR\_START // Y\_ADDR\_START REG=0x0346, 8 REG=0x0348, 2049 // X\_ADDR\_END // Y ADDR END REG=0x034A, 1537 REG=0x034C, 512 // X\_OUTPUT\_SIZE REG=0x034E, 384 // Y OUTPUT SIZE

REG=0x0104, 0 // GROUPED\_PARAMETER\_HOLD

### TN-09-92: Skipping and Binning Modes for the MT9T013 Binning

### **Binning**

The MT9T013 supports 2x1 and 2x2 analog binning (column binning, also called x-binning and row/column binning, also called xy-binning). Binning has many of the same characteristics as skipping, but because it gathers image data from all pixels in the active window rather than a subset of them, it achieves superior image quality and avoids the aliasing artifacts that can be a characteristic side effect of subsampling.

Binning is enabled by selecting the appropriate subsampling settings (x\_odd\_inc=3 and y\_odd\_inc = 1 for x-binning, x\_odd\_inc = 3 and y\_odd\_inc = 3 for xy-binning) and setting the appropriate binning bit in read\_mode (R0x3040-1). As for subsampling, x\_addr\_end and y\_addr\_end may require adjustment when binning is enabled as described in "Programming Restrictions when Skipping" on page 4. Note that it is the first of the two columns/rows binned together that should be the end column/row in binning, so the requirements to the end address is exactly the same as skipping mode. The effect of the different binning settings is shown in Figure 6 and Figure 7 on page 7.

Figure 6: Readout (x\_odd\_inc=3, y\_odd\_inc=1, x\_bin=1)

# TN-09-92: Skipping and Binning Modes for the MT9T013 Binning

Figure 7: Readout (x\_odd\_inc=3, y\_odd\_inc=1, xy\_bin=1)

## TN-09-92: Skipping and Binning Modes for the MT9T013 Binning

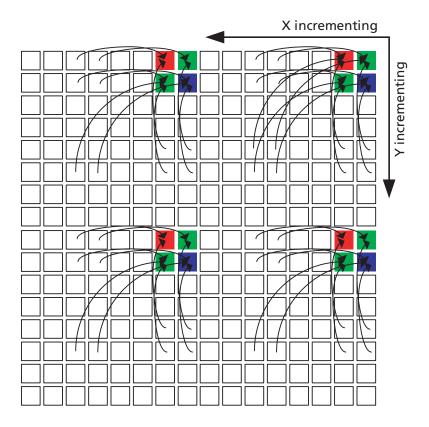

Binning can also be enabled when the 4X subsampling mode is enabled ( $x_odd_inc = 7$  and  $y_odd_inc = 1$  for x-binning,  $x_odd_inc = 7$  and  $y_odd_inc = 7$  for x-binning). In this mode, however, not all pixels will be used so this is not a 4X binning implementation. An implementation providing a combination of skip2 and bin2 is used to achieve 4X subsampling with better image quality. The effect of this subsampling mode is shown in Figure 8 on page 7.

Figure 8: Readout (x\_odd\_inc = 7, y\_odd\_inc = 7, xy\_bin = 1)

#### TN-09-92: Skipping and Binning Modes for the MT9T013 Programming Restrictions when Binning

### **Programming Restrictions when Binning**

Binning requires different sequencing of the pixel array and imposes different timing limits on the operation of the sensor. In particular, xy-binning requires two read operations from the pixel array for each line of output data, which has the effect of increasing the minimum line blanking time.

As a result, when xy-binning is enabled, some of the programming limits declared in the Parameter Limit Registers are no longer valid. In addition, the default values for some of the Manufacturer Specific registers need to be reprogrammed. The recommended settings are shown in Table 1. None of these adjustments are required for binning.

**Table 1: Register Adjustments Required for Binning Mode**

| Register                         | Туре       | Default<br>(normal<br>readout) | Recommended<br>Setting During<br>Binning | Notes                                                                         |

|----------------------------------|------------|--------------------------------|------------------------------------------|-------------------------------------------------------------------------------|

| min_line_blanking_pck            | Read only  | 0x037a                         | 0x0634                                   | Read only register for control software; does not affect operation of sensor. |

| min_line_length_pck              | Read only  | 0x0488                         | 0x0900                                   | Read only register for control software; does not affect operation of sensor. |

| fine_integration_time_min        | Read only  | 0x02b5                         | 0x058d                                   | Read only register for control software; does not affect operation of sensor. |

| fine_integration_time_max_margin | Read only  | 0x01d3                         | 0x0373                                   | Read only register for control software; does not affect operation of sensor. |

| fine_correction                  | Read/write | 0x0100                         | 0x0238                                   | Affects operation of sensor.                                                  |

| fine_integration_time            | Read/write | 0x02b5                         | 0x058d                                   | Normal default is minimum value.                                              |

# TN-09-92: Skipping and Binning Modes for the MT9T013 Sample Register Settings for Binning

#### **Sample Register Settings for Binning**

can be: [x-binning] // GROUPED PARAMETER HOLD REG=0x0104, 1 REG=0x1148, 0x0634 // MIN\_LINE\_BLANKING\_PCK // MIN LINE LENGTH PCK REG=0x1144, 0x0900 REG=0x1008, 0x058D // FINE\_INTEGRATION\_TIME\_MIN REG=0x100A, 0x0373 // FINE\_INTEGRATION\_TIME\_MAX\_MARGIN // FINE\_CORRECTION REG=0x3010, 0x0238 REG=0x3014, 0x058D // FINE INTEGRATION TIME // X\_ADDR\_START REG=0x0344, 8 REG=0x0346, 8 // Y ADDR START // X\_ADDR\_END REG=0x0348, 2053 REG=0x034A, 1543 // Y\_ADDR\_END REG=0x0382, 3 // X ODD INC REG=0x0386, 1 // Y\_ODD\_INC

To achieve a 1024 x 1536 resolution with x-binning, the recommended register settings

REG=0x0104, 0 // GROUPED PARAMETER HOLD

To achieve a 1024 x 768 resolution with xy-binning, the recommended register settings can be:

// GROUPED\_PARAMETER\_HOLD

```

[xy-binning]

REG=0x0104, 1

// GROUPED PARAMETER HOLD

// MIN LINE BLANKING PCK

REG=0x1148, 0x0634

REG=0x1144, 0x0900

// MIN_LINE_LENGTH_PCK

REG=0x1008, 0x058D

// FINE_INTEGRATION_TIME_MIN

REG=0x100A, 0x0373

// FINE_INTEGRATION_TIME_MAX_MARGIN

// FINE CORRECTION

REG=0x3010, 0x0238

REG=0x3014, 0x058D

// FINE_INTEGRATION_TIME_

REG=0x0344, 8

// X ADDR START

REG=0x0346, 8

// Y_ADDR_START

REG=0x0348, 2053

// X_ADDR_END

REG=0x034A, 1541

// Y_ADDR_END

REG=0x0382, 3

// X ODD INC

REG=0x0386, 3

// Y_ODD_INC

BITFIELD=0x3040, 0x0C00, 1

// Enable XY binning

REG=0x034C, 1024

// X OUTPUT SIZE

REG=0x034E, 768

// Y_OUTPUT_SIZE

```

REG=0x0104, 0

### TN-09-92: Skipping and Binning Modes for the MT9T013 Conclusion

#### **Conclusion**

This technical note highlights the skipping and binning features of the MT9T013. For more information on this and other features, refer to the MT9T013 1/4-inch 3.1Mp CMOS digital image sensor data sheet on Micron's Web site at www.micron.com/imaging.

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900 prodmktg@micron.com www.micron.com Customer Comment Line: 800-932-4992 Micron, the M logo, and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

#### TN-09-92: Skipping and Binning Modes for the MT9T013 Revision History

| <b>Revision History</b>             |  |

|-------------------------------------|--|

| Rev. A                              |  |

| <ul> <li>Initial release</li> </ul> |  |